英特尔(Intel)的关键EMIB技术取得了惊人的90%良率,表明其已准备好应用于即将到来的AI数据中心芯片。

英特尔(Intel)EMIB是“芯片怪兽”英特尔(Intel)最关键的代工技术,将使其成为台积电(TSMC)在先进封装领域的竞争对手。我们近期讨论过,AI公司正在关注EMIB,用于其下一代AI芯片。这项技术的目的很简单,就是提供一种比台积电(TSMC)CoWoS技术更具成本效益且可扩展的替代方案。

英特尔(Intel)的先进封装技术将被谷歌(Google)用于其下一代TPU,我们还提到英伟达(NVIDIA)将把EMIB用于其下一代Feynman芯片。广发证券(GF Securities)科技研究分析师杰夫·普(Jeff Pu)分享了对EMIB进展的一些见解,初步印象非常乐观。

据杰夫·普(Jeff Pu)透露,英特尔(Intel)的EMIB良率已达到90%,这对公司代工业务而言是个好消息,也说明了当前市场为何对英特尔(Intel)代工服务如此有信心。Meta(Meta)也被列为EMIB的客户之一,但相关计划涉及一款2028年底的CPU,因此还需更多时间才能获知进一步信息。

与此同时,英特尔(Intel)并未止步于强调EMIB技术的优势。这家芯片制造商再次重点介绍了EMIB(嵌入式多芯片互连桥接)的诸多好处,包括更高的良率、更低的功耗、更低的成本,以及使更大的“混合节点”系统变得实用。

在最新发布的视频中,英特尔(Intel)还分享了一个关于EMIB的有趣见解:EMIB的良率与FCBGA相当,但能提供更高的芯片间互连密度。FCBGA(倒装芯片球栅阵列)是另一种高性能封装技术,用于CPU、GPU及其他控制器芯片等各种IP.FCBGA芯片通过焊球直接连接到PCB基板,而EMIB则将互连线路集成在桥接器内,用于连接多个芯片。

EMIB-M与EMIB-T的关键区别

目前,EMIB技术主要分为两种:EMIB-M和EMIB-T.EMIB-M桥接器专为高效率设计,在硅桥中集成了MIM电容器,通过降低噪声来增强供电性能和完整性。虽然成本略高于金属-氧化物-金属电容器,但MIM(金属-绝缘体-金属)电容器具有更高的稳定性和更低的漏电。

EMIB-M的构建过程涉及通过芯粒创建高密度3D结构。芯粒之间通过EMIB-M桥接器连接,实现高带宽互连,而芯粒的供电线路则绕行桥接器周围。这是一种嵌入式多芯片互连桥接2.5D技术,也是一种高效且经济的方式来连接多个复杂芯片。2.5D封装适用于逻辑-逻辑以及逻辑-高带宽内存(HBM)连接。EMIB-M在桥接器中集成了MIM电容器,而EMIB-T则在桥接器中增加了硅通孔(TSV)。硅桥嵌入封装基板,实现岸对岸连接。EMIB-T可简化从其他封装设计集成IP的难度,供应链和组装流程也因此得到简化。该技术生产已验证,自2017年起已大规模量产,应用于英特尔(Intel)及外部硅芯片。

在EMIB-T中,供电方式发生了改变:通过集成TSV,EMIB-T实现了扩展密度的提升。使用EMIB-T时,供电可以直接通过EMIB桥接器内部进行,而非像EMIB-M那样绕行桥接器外部。EMIB-T旨在满足高性能AI芯片的需求。

面向超大规模云时代的规模化EMIB

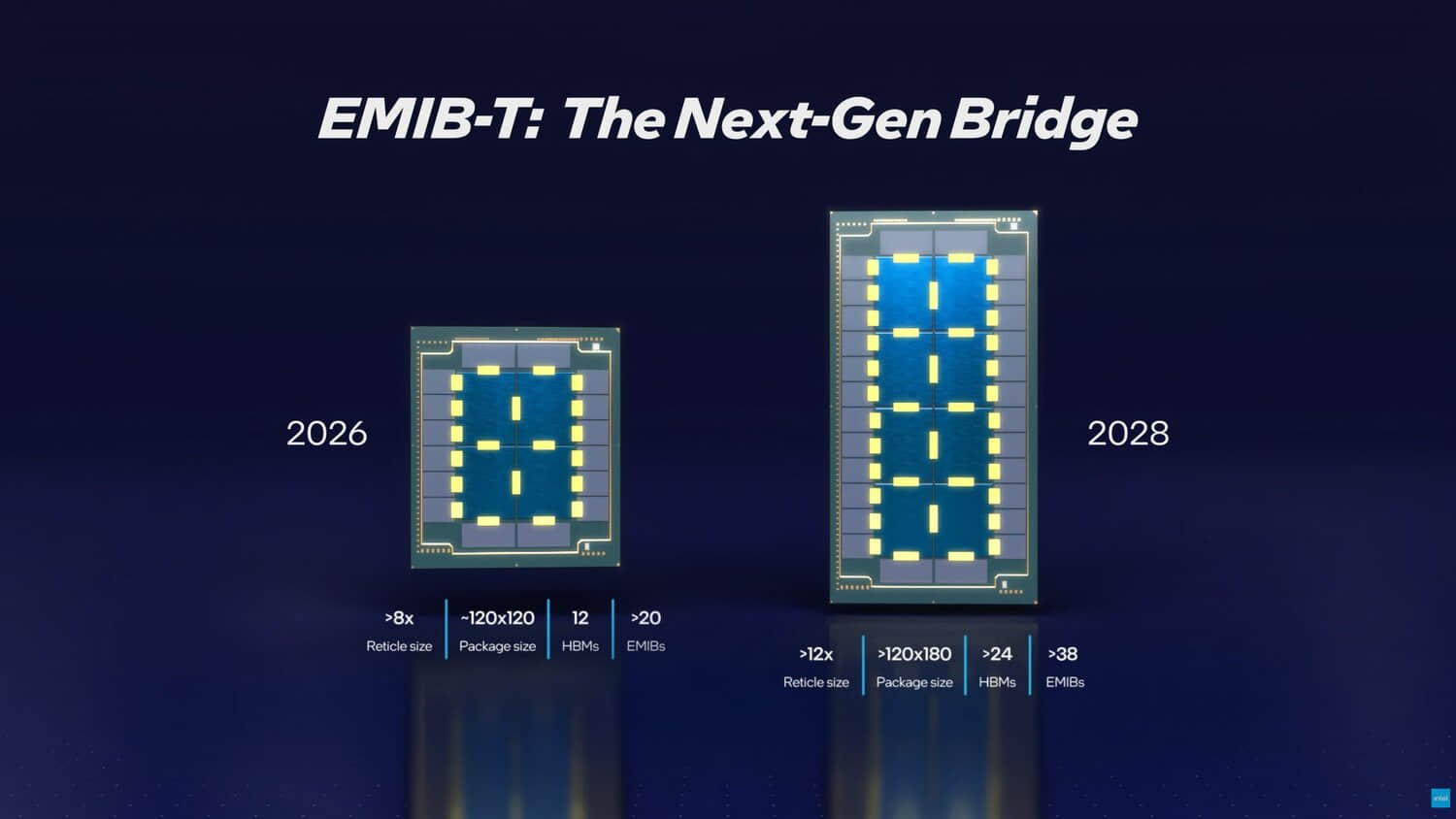

目前,EMIB-T在120x120封装中可实现超过8倍掩模版尺寸的芯片扩展能力,可容纳12个HBM芯片、4个密集芯粒以及超过20个EMIB-T连接。到2028年,英特尔(Intel)计划将扩展能力提升至超过12倍掩模版尺寸,在>120x180封装中容纳超过24个HBM芯片和超过38个EMIB-T桥接器。

作为对比,台积电(TSMC)预计到2028年将达到14倍掩模版尺寸,集成多达20个HBM封装。该公司还推出了SoW(晶圆级系统)封装用于超大型先进封装芯片,不过其成本将远高于CoWoS。

EMIB的一个关键优势在于其IP和工艺节点无关性,因此可以容纳基于不同IP以及各种第三方或内部工艺节点的多个芯片,从而制造出专为带宽、供电完整性和规模而优化的芯片。