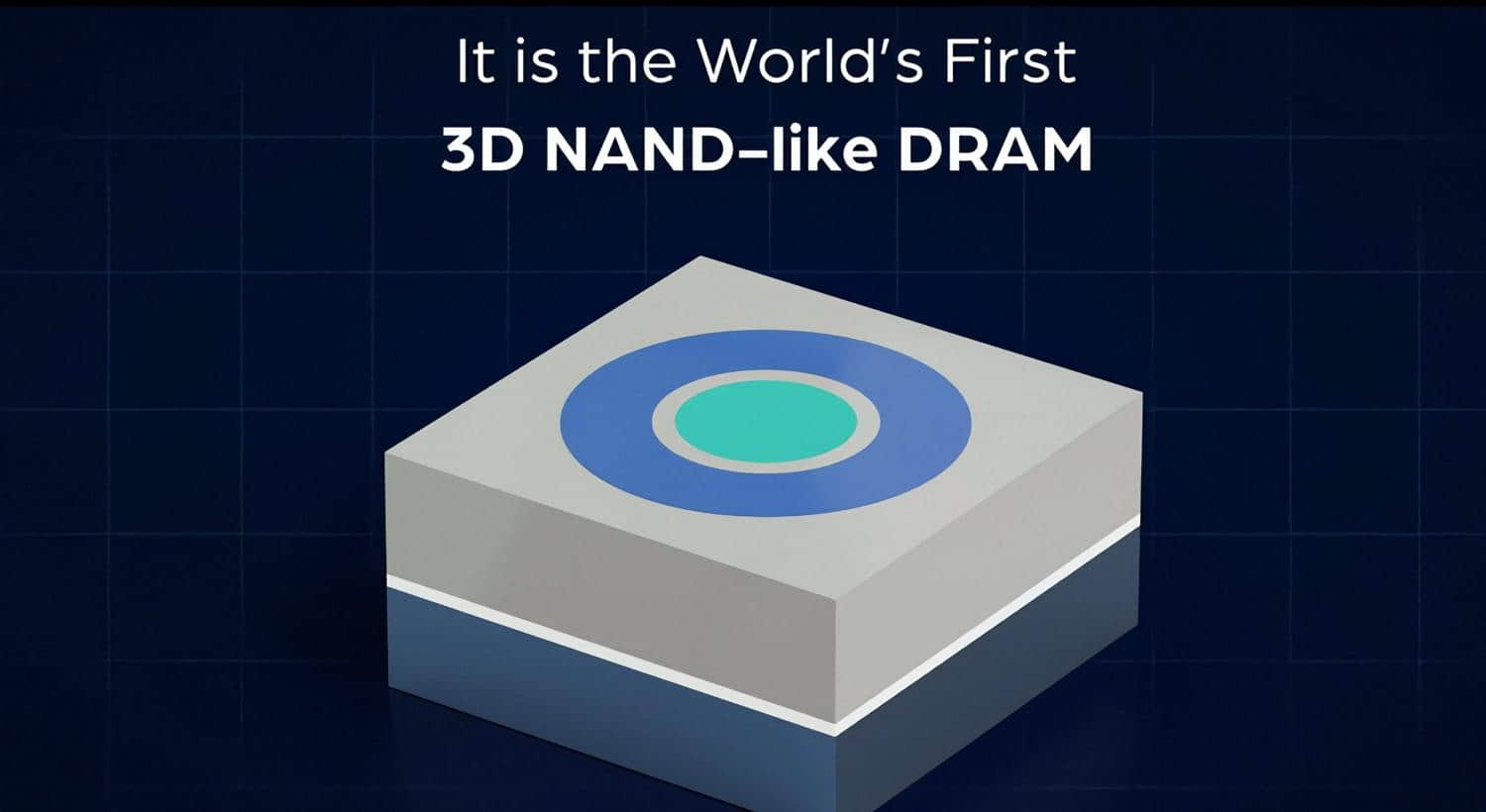

各位可以把DRAM想象成拥有NAND闪存结构的形态,这就是3D X-DRAM的基本概念,它将成为存储市场的一场革命,为人工智能带来更高的密度。

3D X-DRAM 现已更接近现实,它作为HBM的替代方案,为AI提供更高密度。2023年,总部位于美国的NEO Semiconductor公司宣布了其名为“3D X-DRAM”的全新项目,旨在通过采用类似3D NAND的架构来解决DRAM的容量瓶颈问题。该公司还推出了两款3D X-DRAM存储单元,这些单元将被集成到基于3D X-DRAM的存储解决方案中。

这些存储单元包括1T1C和3T0C DRAM单元,最高可实现512Gb的容量,与传统DRAM相比密度提升了10倍,同时具有成本效益且适合高良率生产。每种3D X-DRAM变体都针对不同用途设计。例如,1T1C与主流DRAM及HBM路线图兼容,可提供高密度DRAM,而3T0C则非常适合AI工作负载。

1T1C(一晶体管一电容):高密度DRAM的核心解决方案,与主流DRAM和HBM路线图完全兼容。

3T0C(三晶体管零电容):针对电流感测操作进行了优化,是AI和存内计算的理想选择。

1T0C(一晶体管零电容):一种浮体单元结构,适用于高密度DRAM、存内计算、混合存储和逻辑架构。

本次发布的主要特点包括:

无与伦比的保持力和效率:得益于IGZO沟道技术,1T1C和3T0C单元的仿真数据显示其数据保持时间长达450秒,大幅降低了刷新功耗。

仿真验证:TCAD(计算机辅助设计技术)仿真确认了其快速的10纳秒读写速度以及超过450秒的数据保持时间。

易于生产:采用经过改良的3D NAND工艺,只需极少的改动即可实现全面扩展,并能快速集成到现有的DRAM产线中。

超高带宽:采用独特的阵列架构进行混合键合,在降低功耗的同时显著提升了内存带宽。

面向高级工作负载的高性能:专为AI、边缘计算和存内处理而设计,提供可靠的高速访问并降低能耗。

DRAM相较于HBM的一个优势在于,尽管高带宽内存(HBM)是AI和高性能计算领域的首选,但它生产困难、成本高昂,并且在部署到服务器芯片之前需要大量的测试和验证。相比之下,DRAM易于生产,且无需进行同样多的检查。此外,3D X-DRAM在单个晶片内采用类似单片的架构,而非像HBM那样将多个DRAM晶片堆叠在一起。

如今,NEO Semiconductor公司已经展示了3D X-DRAM的概念验证(POC),并获得了进一步推进该项目的投资。借助这些POC测试芯片,该公司已经证明,可以利用现有的3D NAND基础设施来制造3D X-DRAM,其方式是增加多层DRAM,而非像HBM那样进行堆叠。

POC测试芯片的首批测试结果如下:

读写延迟:<10 ns

数据保持时间:85°C下大于1秒(比JEDEC标准的64毫秒提升了15倍)

位线干扰:85°C下大于1秒

字线干扰:85°C下大于1秒

耐久性:大于10¹⁴次循环

随着AI和高性能计算领域对内存需求的增长,先进的DRAM解决方案将变得不可或缺。为此,英特尔(Intel)也在准备一种类似的DRAM架构,名为ZAM(Z-Angle Memory,Z角度内存)。目前,这两种DRAM架构都远未进入量产阶段,但鉴于它们所取得的进展以及主要企业的持续投资,我们有望在十年内看到这些技术为服务器领域提供动力。