推理已成为计算供应商的下一个重点领域。在英伟达(NVIDIA)与格罗克(Groq)建立合作关系后,人工智能行业意识到其需求远不止图形处理器(GPU)。这促成了一对新组合的出现:英特尔(Intel)和桑巴诺瓦(SambaNova)。

英特尔(Intel)的至强(Xeon)6处理器将作为智能体系统的主机,并由桑巴诺瓦(SambaNova)的SN50芯片负责解码工作。

在今年的GTC大会上,我们看到英伟达(NVIDIA)谈论了分解式推理,以及作为制造商,从“唯GPU论”思维转向,将相对较新的计算单元形式引入基础设施竞争,对他们而言变得多么重要。随着与格罗克(Groq)的授权协议达成,我们看到基于静态随机存取存储器(SRAM)的语言处理单元(LPU)在鲁宾(Rubin)的LPX机架中首次亮相。如今,英特尔(Intel)和桑巴诺瓦(SambaNova)决定尝试类似方案,公布了一种新的“推理架构”,该架构结合了桑巴诺瓦(SambaNova)的再配置数据流单元(RDU)与英特尔(Intel)的至强(Xeon)6处理器。

桑巴诺瓦(SambaNova)今日宣布了与英特尔(Intel)合作的下一阶段:一种异构硬件解决方案,结合了用于预填充任务的GPU、兼具主机和“执行”中央处理器(CPU)功能的英特尔® 至强® 6处理器,以及用于解码任务的桑巴诺瓦(SambaNova)再配置数据流单元(RDU),旨在为要求最苛刻的智能体人工智能应用提供优质的推理性能。

这种安排的目标是让再配置数据流单元(RDU)专注于解码工作负载,GPU处理预填充工作,而至强(Xeon)6处理器则处理编排和通用任务等。英特尔(Intel)-桑巴诺瓦(SambaNova)的合作并未锁定特定的超大规模云服务商作为GPU选项,这意味着也可以在此配置中集成专用集成电路(ASIC),尽管桑巴诺瓦(SambaNova)没有详细说明GPU的具体性能。桑巴诺瓦(SambaNova)将集成其SN50单元(我们稍后会讨论),同时该公司表示,与ARM选项相比,他们发现至强(Xeon)6处理器是“端到端编码智能体工作流”的理想选择。

我们来谈谈SN50芯片。该解决方案于2026年初公布,采用了该公司第五代再配置数据流单元(RDU),并集成了动态随机存取存储器(DRAM)、静态随机存取存储器(SRAM)和高带宽存储器(HBM)。SN50拥有2TB的DDR5内存,以及64 GB的HBM3和520 MB的静态随机存取存储器(SRAM)。如果你已经猜到,那么采用这种片上内存架构的理念就是为了提供极低的延迟、高吞吐量和巨大的容量。SN50可能是唯一采用这种内存布局的加速器。据制造商称,动态随机存取存储器(DRAM)+ 静态随机存取存储器(SRAM)+ 高带宽存储器(HBM)的组合创造了“智能体缓存”。

在更宏观的层面上,英特尔(Intel)与桑巴诺瓦(SambaNova)合作的方式和英伟达(NVIDIA)的主要区别在于,前者更侧重于一个“更安全”的赌注,因为它无需为分解式推理提供庞大的底层基础设施。对于寻求更模块化、针对“预填充+解码”分解的机架级解决方案的超大规模云服务商来说,英特尔(Intel)-桑巴诺瓦(SambaNova)选项是一个不错的选择。我们曾预期英特尔(Intel)会在再配置数据流单元(RDU)集成方面走得更深,但目前看来,可能仅限于将至强(Xeon)中央处理器(CPU)作为主机选项。

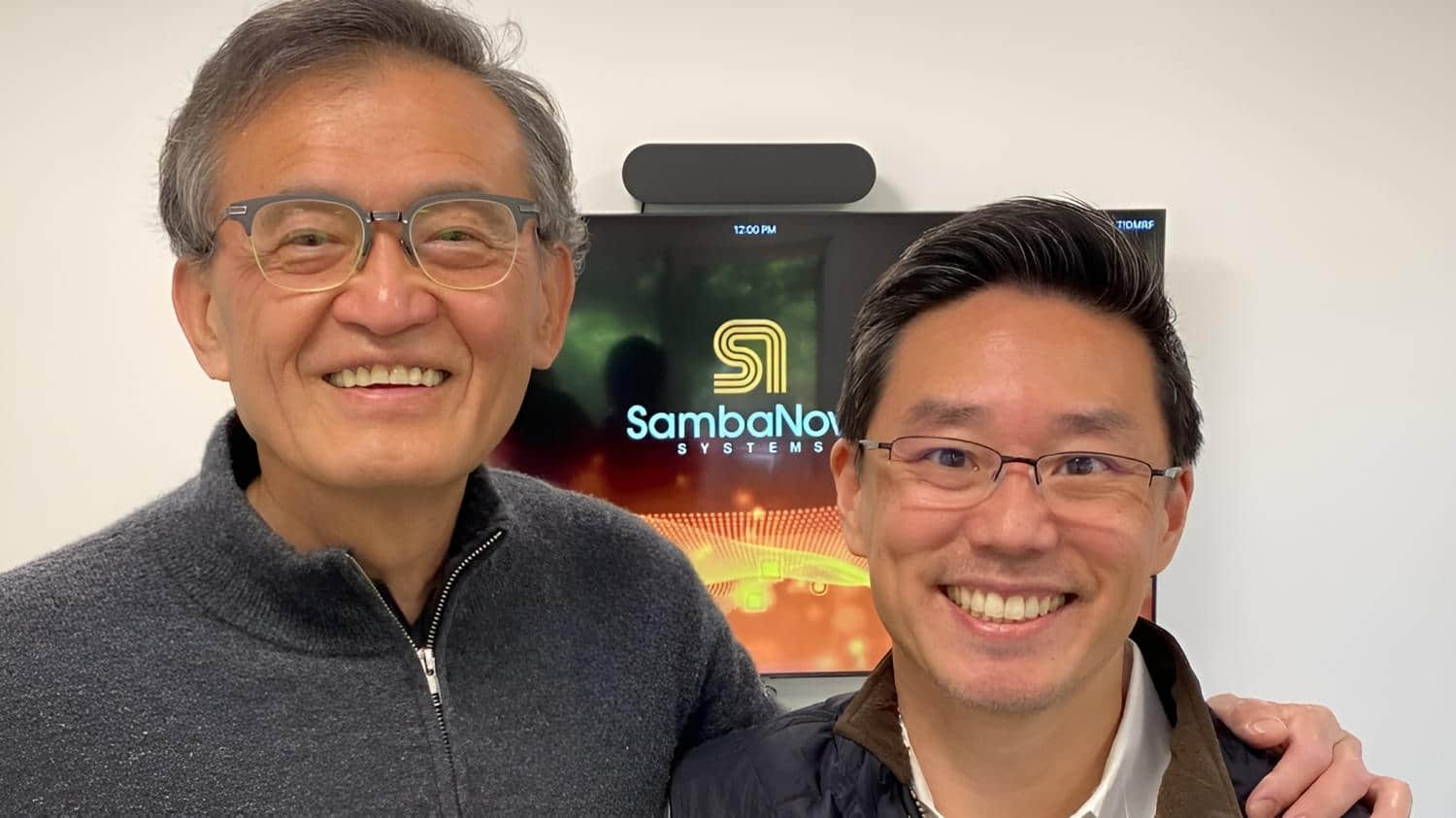

英特尔(Intel)的首席执行官参与了桑巴诺瓦(SambaNova)的最新一轮融资,而厉成宾(Lip-Bu Tan)也是该公司的早期投资者。此前曾有收购该公司的计划,但据报道因董事会意见分歧而中止,这就是为什么英特尔(Intel)最终选择作为融资参与方。