负责定义行业标准内存规格的组织JEDEC即将敲定一项名为SPHBM4的新内存标准,该标准旨在通过与传统有机基板的兼容性,以“窄”512位接口提供完整的HBM4级带宽、更高容量和更低的集成成本。如果这项技术取得成功,将填补HBM所能服务的市场中的许多空白,但正如我们将在下文中解释的那样,它不太可能成为GDDR内存的杀手。

虽然高带宽内存(HBM)的1024位或2048位接口能带来无与伦比的性能和能效,但这类接口会占用高端处理器内部大量宝贵的芯片面积,从而限制了每个芯片上的HBM堆栈数量,进而影响了AI加速器支持的内存容量。这不仅影响单个加速器的性能,也影响使用它们的大型集群的能力。

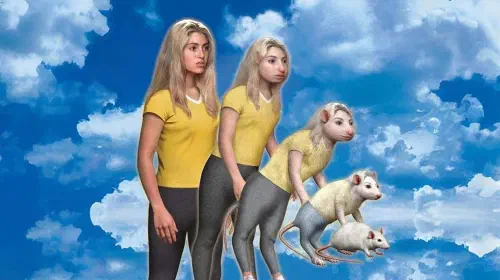

标准封装中的HBM

标准封装高带宽内存(SPHBM4)通过将HBM4内存接口宽度从2048位减少到512位,并采用4:1串行化来维持相同的带宽,从而解决了这个问题。JEDEC并未明确说明“4:1串行化”是指将数据传输速率从HBM4的8 GT/s提升四倍,还是引入一种具有更高时钟频率的新编码方案。不过,其目标显而易见:在512位接口下保持HBM4的总带宽。

在内部,SPHBM4封装将使用行业标准的基底芯片(可能由采用逻辑制造工艺的代工厂生产,因此成本不会更低,因为将“宽”DRAM芯片路由到“窄”基底芯片在密度方面可能会变得棘手,并且由于来自DRAM的慢速布线和来自基底芯片本身的快速布线,将带来时钟同步挑战)。它还将使用标准的HBM4 DRAM芯片,这简化了控制器开发(至少在逻辑层面),并确保每个堆栈的容量与HBM4和HBM4E保持一致,每个HBM4E堆栈最高可达64 GB。

理论上,这意味着SPHBM4的内存容量将是HBM4的四倍,但实际上,随着每次新工艺技术的推出,芯片面积成本越来越高,AI芯片开发商可能会在内存容量、更高的计算能力以及他们能集成到芯片中的多功能性之间寻求平衡。

GDDR7的杀手?

热心的读者可能会问,为什么不将SPHBM4内存用于游戏GPU和显卡呢?与GDDR7或可能采用PAM4编码的GDDR7X相比,这可以在成本适度增加的情况下实现更高的带宽。

SPHBM4旨在提供HBM4级带宽,其基本设计理念是优先考虑性能和容量,而非功耗和成本等其他因素。

虽然比HBM4或HBM4E便宜,但SPHBM4仍然需要堆叠式HBM DRAM芯片,这些芯片物理尺寸更大,因此比商用DRAM芯片更昂贵,此外还需要接口基底芯片、硅通孔(TSV)处理、已知合格芯片流程以及先进的封装内组装。与受益于庞大的消费和游戏市场销量、简单封装和成熟PCB组装工艺的商用GDDR7相比,这些步骤主导了成本,并且在大规模生产时成本下降幅度有限。

也就是说,用单个先进的SPHBM4取代多个GDDR7芯片可能不会降低成本,反而可能增加成本。

关键在于实施细节

虽然512位内存总线仍然是一个复杂的接口,但JEDEC表示,SPHBM4支持在传统的有机基板上进行2.5D集成,且不需要昂贵的硅中介层,从而显著降低了集成成本,并可能扩大设计灵活性。同时,凭借行业标准的512位接口,与依赖UCIe或专有接口的C-HBM4E解决方案相比,SPHBM4可以提供更低的成本(这得益于标准化带来的规模效应)。

与基于硅的解决方案相比,有机基板布线使得SoC与内存堆栈之间的电气通道长度可以更长,这可能缓解大型封装中的布局限制,并且比目前可能实现的方案在封装附近容纳更多的内存容量。尽管如此,很难想象使用传统基板来布线3084位内存接口(以及数据和电源布线),但我们将拭目以待。