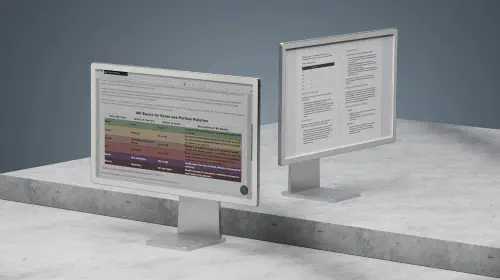

提到处理器时,人们通常会联想到小巧的芯片。但台积电(TSMC)正在开发的CoWoS技术新版本,将支持合作伙伴构建尺寸达9.5倍光罩(7,885平方毫米)的多芯片组合体,其采用的120×150毫米基板(18,000平方毫米)面积甚至略大于标准CD盒。台积电表示,这些庞然大物的性能可达传统处理器的40倍。

从巨无霸到超级巨无霸

目前台积电CoWoS技术可支持最大2,831平方毫米的中介层,约为其光罩限制(极紫外标准858平方毫米,台积电采用830平方毫米)的3.3倍。AMD的Instinct MI300X加速器与英伟达(Nvidia)B200 GPU等产品已采用该技术,将两片大型逻辑芯片与八组HBM3/HBM3E内存堆栈集成。但这对未来应用仍显不足。

台积电计划在明年或稍晚推出新一代CoWoS-L封装技术,支持4,719平方毫米的中介层(标准光罩面积的5.5倍)。该封装可容纳12组高带宽内存堆栈,需采用100×100毫米(10,000平方毫米)的更大基板。基于此的解决方案预计带来超3.5倍于现有设计的运算性能。虽然能满足英伟达搭载12组HBM4的Rubin GPU需求,但性能更强的处理器仍需更大规模集成。

更长远来看,台积电计划推出7,885平方毫米的中介层(光罩限制的9.5倍),搭载于120×150毫米基板。相比去年公布的120×120毫米基板8倍光罩方案,此次升级显然源自客户需求。此类封装预计支持四组3D堆叠系统级集成芯片(如N2/A16芯片堆叠于N3逻辑芯片之上)、十二组HBM4内存堆栈及额外输入输出芯片。

极致性能的追求

对于追求极致性能的客户,台积电提供晶圆级集成的系统级晶圆(SoW-X)技术。目前仅有Cerebras和特斯拉(Tesla)将其用于AI处理器WFE与Dojo,但台积电预计将出现更多类似需求客户。

电力输送挑战

构建9.5倍光罩或晶圆级处理器难度极高。这些多芯片方案需要千瓦级高电流供电,对服务器制造商和芯片开发者构成严峻挑战,必须从系统层面解决。台积电在2025技术研讨会上提出了千瓦级高效供电方案。

台积电计划将基于N16 FinFET工艺的 monolithic电源管理IC(PMIC)与硅通孔(TSV)、晶圆级电感直接集成至采用RDL中介层的CoWoS-L封装中,通过基板实现电力输送。这种设计缩短了电源与活性芯片的距离,降低寄生电阻并提升系统供电稳定性。

基于N16的PMIC可精准控制动态电压调节(DVS),供电密度达传统方案的5倍。中介层或硅基板中嵌入的深沟槽电容(eDTC/DTC)提供高达2,500 nF/mm²的去耦密度,有效滤除电压波动,确保快速负载变化下的稳定运行。这种嵌入式设计对多核/多芯片架构的能效管理至关重要。

台积电的供电方案体现了系统级协同优化趋势——将电力输送视为芯片、封装与系统设计的有机整体,而非独立功能模块。

形态与散热革命

中介层尺寸暴增将重塑系统设计。100×100毫米基板已接近OAM 2.0规格(102×165毫米)的物理极限,而120×150毫米方案必然催生新的模块封装与电路板布局标准。

除物理限制与功耗外,这些巨型多芯片系统级封装(SiP)会产生惊人热量。硬件厂商已开始探索直接液体冷却(如英伟达GB200/GB300 NVL72采用的技术)与浸没式冷却等方案。但台积电坦言,目前尚无法在芯片或SiP层面解决散热问题。