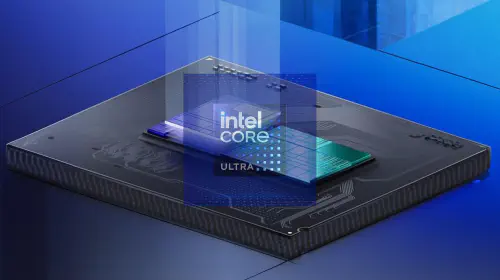

AMD正式确认,其基于Zen 6架构的下一代EPYC威尼斯(Venice)处理器将采用台积电(TSMC)最先进的2纳米制程节点N2技术。这一里程碑式合作标志着两家企业在先进制程与创新架构协同优化方面取得重大突破。

根据官方声明,代号为“第六代威尼斯”的EPYC处理器将成为业界首款基于台积电N2(2纳米)制程节点流片成功的高性能计算产品。台积电将采用纳米片(NanoSheet)晶体管技术制造这些芯片,并与AMD的Zen 6及Zen 6C架构进行深度协同优化,预计新产品将于明年正式发布。

值得注意的是,AMD还宣布已在台积电亚利桑那州21厂(Fab 21)成功完成第五代EPYC处理器的验证工作。这对积极推进半导体本土化制造的美国而言具有重要战略意义。

AMD董事会主席兼首席执行官苏姿丰博士表示:“台积电是我们多年的核心合作伙伴,通过与对方研发制造团队的深度协作,AMD得以持续推出突破高性能计算边界的产品。作为台积电N2制程和亚利桑那工厂的首批高性能计算客户,双方正携手推动计算技术的未来革新。”

台积电董事长刘德音博士回应称:“我们非常荣幸AMD成为2纳米先进制程和亚利桑那晶圆厂的领航客户。通过紧密合作,双方正在实现显著的技术升级,为高性能芯片带来更卓越的能效表现。”